Anwendung von differentiellen Quarzoszillatoren in Hochgeschwindigkeits-FPGAs

2025-07-10

Anwendung differentieller Quarzoszillatoren in Hochgeschwindigkeits-FPGAs

Differentielle Quarzoszillatoren sind entscheidend für Hochgeschwindigkeits-FPGA-Designs, insbesondere in Systemen mit hohen Anforderungen an:

·Hochgeschwindigkeits-Schnittstellen: PCIe, SFP+/QSFP, 10G/25G/40G/100G Ethernet, DDR4/DDR5

·Mehrkanalige Datenerfassungssysteme

·Hochgeschwindigkeitskommunikation (SerDes-basiert)

·Präzise Synchronisationssysteme (Zeitstempelung, ADC/DAC-Taktansteuerung)

I. Definition differentieller Quarzoszillatoren

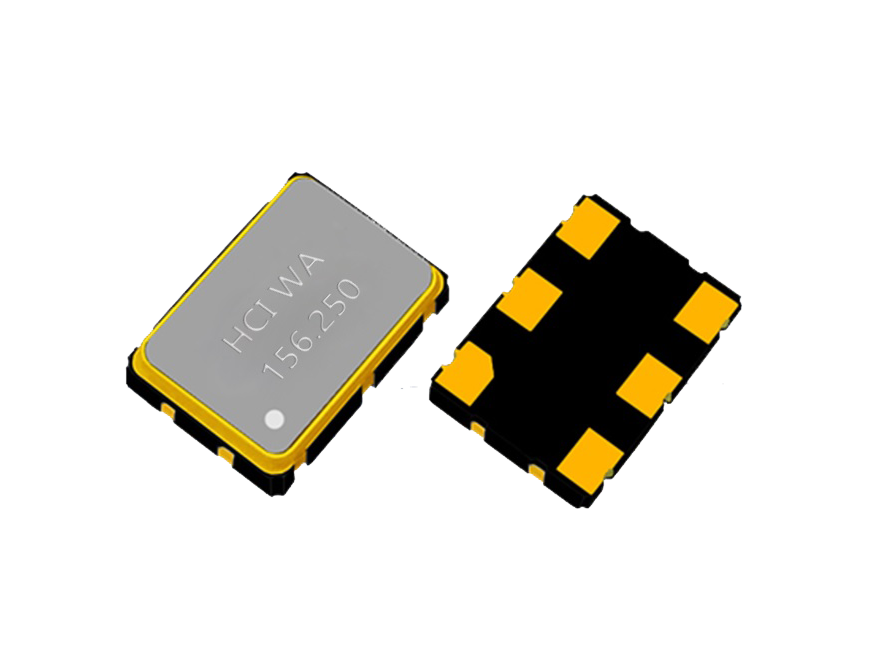

Ein differenzieller Quarzoszillator ist ein aktiver Oszillator mit differentiellen Ausgangssignalen (z.B. LVDS, LVPECL, HCSL), der zwei gegenphasige Taktsignale (CLK+ und CLK−) erzeugt. Im Gegensatz zu traditionellen einzeln-endenden Oszillatoren (z.B. CMOS-Ausgangstypen).

II. Vorteile differentieller Signalführung

Merkmal | Differentielles Signal | Einzeln-endendes Signal |

Störfestigkeit | Hoch (Gleichtaktstörunterdrückung) | Niedrig |

Signalintegrität | Hervorragend (für Hochgeschw.-Übertrag.) | Gering |

Treiberstärke | Hoch (lange Leitungen/Hochgeschw.) | Begrenzt |

Jitter-Verhalten | Überlegen (geringeres Phasenrauschen) | Ungünstiger |

III. Anwendungen in Hochgeschwindigkeits-FPGAs

1.Referenztakt für Hochgeschwindigkeits-Schnittstellen

Erforderlich für PCIe, 10G/25G Ethernet, SATA

Standardfrequenzen: 100 MHz oder 156,25 MHz (HCSL/LVDS-Ausgänge)

Wird von FPGA-Transceiverblöcken (GTX/GTH/GTP) benötigt

Typische Verbindung:

Differenzieller Oszillator → FPGA GTREFCLK0/1-Pins

2.Kern-Taktquelle für Taktverteilungsbäume

Steuert Taktverteiler-ICs (SI5341/AD9528) für synchronisierte Mehrkanal-Takte

Kritisch für Taktausrichtung in Multi-ADC/DAC/FPGA-Systemen

Struktur:

Differenzieller Oszillator → Taktmanager (PLL/Fanout Buffer)

↓

Synchronisierte Takte → FPGA/ADC/DAC

3.Ansteuerung interner FPGA-PLLs/MMCMs

Liefert hochwertige Taktinputs via differentieller Eingänge (z.B. IBUFDS) Interne PLLs/MMCMs erzeugen Systemtakte und reduzieren globales Jitter

FPGA-Kompatibilität differentieller Ausgangsstandards

Ausgangstyp | Anwendungen | FPGA-Kompatibilität |

LVDS | Universell | Universell unterstützt (GTX/GTH-Eingänge) |

HCSL | PCIe, Server-Hauptplatinen | Native Unterstützung (z.B. Xilinx PCIe-IP) |

LVPECL | HF-Anwendungen | Externe Beschaltung erforderlich |

CML | Ultrahochgeschwindigkeit | High-End-FPGA-Transceiver unterstützen |

✔ Ausgangstyp gemäß FPGA-Herstellerempfehlung wählen

IV. Auswahlkriterien

Parameter | Spezifikation |

Frequenzstabilität | ≤±25 ppm (oder enger) |

Phasenjitter (12k–20MHz) | <0,5 ps RMS (>10G-Schnittstellen) |

Ausgangstyp | LVDS/HCSL (FPGA-kompatibel bevorzugt) |

Lasttreiberfähigkeit | ≥15 pF (an nachgelagerte Komponenten anpassen) |

Temperaturbereich | Industriebereich (–40 °C bis +85 °C) |

Protokollspezifische Frequenzen:

PCIe: 100 MHz

10G Ethernet/SFP+: 156,25 MHz

25G/40G Ethernet: 312,5 MHz

JESD204B/C: 250/312,5/625 MHz

FPGA-Datenblätter für Taktanforderungen konsultieren

Jitter-Anforderungen müssen streng eingehalten werden:

RMS-Jitter < 0,5 ps (für Hochgeschwindigkeitsschnittstellen)

Besonders kritisch für PCIe, JESD204C und 10G/25G-Ethernet

V. Typische Anwendungsfrequenzen

Frequenz (MHz) | Anwendungen | Hinweise |

100,000 | PCIe Gen1-5, Logiksysteme | Industriestandard HCSL/LVDS |

125,000 | Gigabit Ethernet (SGMII) | GMII/SGMII-Kompatibilität |

156,250 | 10G Ethernet, SFP+, QSFP | Kern-SerDes-Frequenz |

200,000 | DDR4-Referenztakt | PLL-Vervielfachungsbasis |

212,500 | JESD204B/C-Datenwandler | Präzisionssysteme |

250,000 | Hochgeschw.-ADC/DAC | Ultrageringes Jitter kritisch |

312,500 | 25G Ethernet, optische Netze | CML/LVPECL-Ausgänge typisch |

322,265625 | CPRI Option 6 (6,144 Gbps) | Funkinfrastruktur |

644,53125 | CPRI Option 10 (12,288 Gbps), JESD204C | Femtojitter erforderlich |

✔ Gerätespezifische Beratung: Hangjing Vertrieb/Technik

VI. Zusammenfassung der Kernvorteile

Eigenschaft | Nutzen |

Genauigkeit | Geringes Jitter, hohe Frequenzstabilität |

Störfestigkeit | Robuste Gleichtaktunterdrückung |

Geschwindigkeit | GHz-Übertragungsfähigkeit |

Anwendungen | PCIe, Ethernet, DDR4/5, JESD204B/C, ADC/DAC-Synchronisation |

Fazit: Differentielle Quarzoszillatoren sind für moderne Hochgeschwindigkeits-FPGA-Systeme unverzichtbar und gewährleisten zuverlässige Hochgeschwindigkeitskommunikation.

Technischer Support:Für FPGA-spezifische Implementierungen (Xilinx Zynq UltraScale+, Intel Stratix 10) oder Schnittstellenanforderungen (PCIe Gen3/SFP+/JESD204C) bietet Suzhou Hangjing optimierte Taktlösungen und Schaltplanberatung.

Kristalloszillator,XO,Differential-Kristalloszillator ,Hochgeschwindigkeits-FPGA,FPGA

Nächste Seite

Scannen, um WeChat hinzuzufügen

Scannen, um WeChat hinzuzufügen